AI 시대가 도래하면서, 그래픽 처리 장치(GPU)와 같은 고성능 컴퓨팅 디바이스의 중요성이 증가하고 있습니다. 이러한 디바이스는 대량의 데이터를 빠르게 처리하는 능력이 필요하며, 이를 가능하게 하는 핵심 요소 중 하나가 바로 반도체 패키지 기술입니다. 특히나 최근 들어 Nvidia GPU가 시장에 주목을 받으며 이를 생산하는 기술 CoWoS(Chip on Wafer on Substrate)와 같은 2.5D 패키지 기술이 다양하게 소개되어 있다.

논문 리뷰하기 전에 왜 2.5D 패키지 기술이 필요한가에 대한 이해가 필요하다.

기존 Multichip 구조인 2D package와 HBM과 같이 TSV로 위아래 칩이 연결된 3D package, Interposer를 사용해서 고밀도의 칩을 2D와 같이 연결하고 TSV를 적용하여 I/O를 다시 연결하는 방식을 2.5D package라고 한다.

최근 다양한 방식의 2.5D가 적용되는 이유는 HBM과 ASIC chip을 연결할 수 있는 방식이 기존 substrate로 한계가 있기 때문이다. HBM과 ASIC을 연결하기 위해선 Line/space 가 2/2um 이하가 되어야 하는데 현재 substrate 공정방식으로는 2/2um 양산이 어려운 방식이다. L/S 외에도 고밀도 package의 적용되는 25um Cu pillar bump를 50um pitch 수준으로 연결할 수 pad 형성도 불가능한 수준이다. 물리적인 연결 외에도 다양한 제한 사항으로 Interposer를 적용해야만 2.5D package를 완성할 수 있다. 현재 대부분의 2.5D 제품은 Silicon inteposer를 사용하고 있는데 비용과 공급 문제로 Silicon Inteposer 외에 2.5D 연결 방식을 찾기 위해 많은 회사에서 다양한 아이디어를 제시하고 있다.

위 관련하여 논문에서는 RDL을 사용한 interposer package와 Si interposer 2.5D package를 비교 분석하였다.

1. Package structure

논문에 소개된 RDL Interposer 구조는 총 3가지 이다. Fan out chip on substrate chip first, Chip last와 Stacking Fan out chip on substrate인데, 이름은 다르지만 Package를 하는 회사에서 다양한 이름으로 이러한 3가지 접근방식으로 2.5D 패키지를 개발과 양산을 하고 있다.

Chip first는 Chip attach 공정과 몰드공정 후 바로 그 위에 RDL을 형성하여 Chip과 RDL을 solder bump가 reflow 방식으로 연결하는 게 아닌 Photo litho. 공정 연결이 되기 때문에 Chip bump가 없다. Interconnection이 짧아지고 두께가 얇아지는 장점이 있지만 Good die를 전면에 모두 사용이 필요하여 RDL 공정 후 fail 영역 chip을 사용하지 못하는 단점이 있다.

Chip last는 RDL을 먼저 완성 후 Wafer level package 공정과 동일하게 assembly 공정을 진행하게 된다. RDL AOI 후 Good 영역에만 chip을 붙일 수 있다는 장점이 있다.

Stacking FOCoS는 bridge die를 사용하여 고밀도로 연결이 필요한 영역만 고밀도를 적용하여 연결하고 그렇지 않은 영역은 Line/Space를 크게 하여 공정 비용을 절감할 수 있다.

2. Package assembly process

패키지 구조에 따라 위 그림과 같은 assembly 공정 순서를 논문에서 확인 할 수 있다.

4.Results

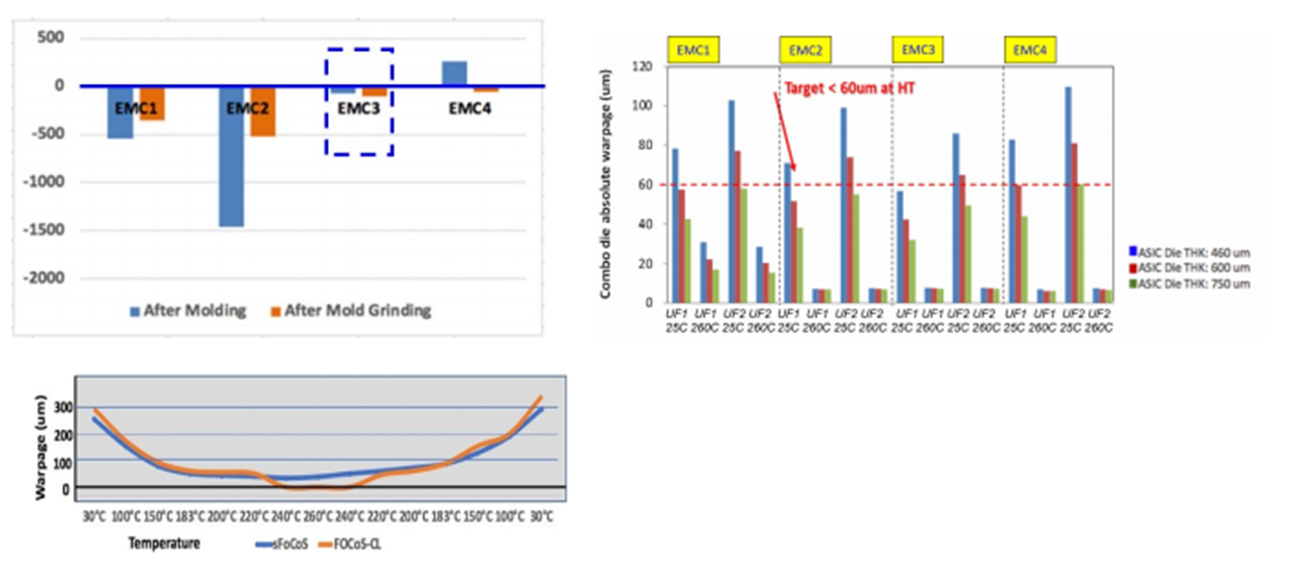

RDL inteposrt 적용 패키지에서는 warpage issue가 가장 큰 issue가 될 수 있어 EMC와 underfill 조합으로 최적의 warpage를 갖는 material 조합과 신뢰성 test를 진행하였다.

논문에 EMC, UF property에 대해 실제 값이 나오지는 않고 비교값으로 대체하여 표기되어 있다. warapge 측정결과를 확인하였을 때, 최적의 조합인 EMC3과 UF1을 적용하여하였을 때 신뢰성 test 진행결과는 아래와 같이 확인되었다.

4가지 구조 모두 일정 수준이상에 신뢰성 조건은 pass 하였고 3가지 중에서는 chip last 구조가 가장 우수한 것으로 확인되는데 논문상 이와 관련된 comment는 없었다.